# **Intel® Ethernet Fabric Suite Fabric Host Software**

**User Guide**

Rev. 1.11

June 2025

You may not use or facilitate the use of this document in connection with any infringement or other legal analysis concerning Intel products described herein. You agree to grant Intel a non-exclusive, royalty-free license to any patent claim thereafter drafted which includes subject matter disclosed herein.

No license (express or implied, by estoppel or otherwise) to any intellectual property rights is granted by this document.

All product plans and roadmaps are subject to change without notice.

The products described may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Intel technologies may require enabled hardware, software or service activation.

No product or component can be absolutely secure.

Your costs and results may vary.

Intel, the Intel logo, and other Intel marks are trademarks of Intel Corporation or its subsidiaries. Other names and brands may be claimed as the property of others.

Copyright  $^{\scriptsize @}$  2020–2024, Intel Corporation. All rights reserved.

## **Revision History**

| June 2025   1.11   Product 12.1.0.0 release - Changes to this document include:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | June 2025 1.11 Product 12.1.0.0 release - Changes to this document include:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |               |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| Improved PSM3_FLOW_CREDITS to have a better flow control for RC verbs   Improved PSM3_MTU to allow a value larger than NIC MTU for RC verbs   Removed selection 0x10 from PSM3_TRACEMASK     Product 11.7.0.0 release - Changes to this document include:   Default for PSM3_RDMA is now 1 when rendezvous module is available or PSM3_GPUDIRECT is enabled.   PSM3_FLOW_CREDITS now allows dynamic credit adjustment based on network behavior.   Default for PSM3_MQ_RNDV_SHM_GPU_THRESH is now 63 for NVIDIA GPUs.    March 2024   1.8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | connection recovery, see PSM3 Verbs RDMA Modes and Rendezvoor Module. As part of this, PSM3_RV_RECONNECT_TIMEOUT is deprecated and replaced with PSM3_RECONNECT_TIMEOUT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2025 1.11     |

| Default for PSM3_RDMA is now 1 when rendezvous module is available or PSM3_GPUDIRECT is enabled.  PSM3_FLOW_CREDITS now allows dynamic credit adjustment based on network behavior.  Default for PSM3_MQ_RNDV_SHM_GPU_THRESH is now 63 for NVIDIA GPUs.  March 2024  1.8  Product 11.6.0.0 release - Changes to this document include:  Added new GPU aware NIC selection algorithms. See Multi-Rail Environment Variables, Multi-IP Configuration Examples, PSM3 Multi-IP Configuration Examples, Building the PSM3_RMM, PSM3_MULTIRAIL, PSM3_MULTIRAIL_MAP, and PSM3_MULTIRAIL_PSM3_MULTIRAIL_MAP, and PSM3_MULTIRAIL_PSM3_MULTIRAIL_MAP, and PSM3_MULTIRAIL_PSM3_MULTIRAIL_MAP, and PSM3_MULTIRAIL_PSM3_MULTIRAIL_MAP, and PSM3_MULTIRAIL_PSM3_MULTIRAIL_MAP now allows for per process selection of NICs. Also updated Multi-Rail Environment Variables, Multi-Rail Configuration Examples, and PSM3_Multi-IP Environment Variables.  Documented Intel MPI support of NVIDIA GPUs, see Using PSM3 Features for NVIDIA GPUDIrect.  Documented Intel MPI support of NVIDIA GPUS, see Using PSM3 Features for NVIDIA GPUDIrect.  Documented Intel MPI support of NVIDIA GPUS, see Using PSM3_GPUDIRECT Access to Intel GPUs, Using PSM3_Features for NVIDIA GPUDIrect, and PSM3_GPUDIRECT.  Changes to default for PSM3_GPUDIRECT RDMA_RECV_LIMIT and PSM3_GPUDIRECT_RDMA_SEND_LIMIT for Intel GPUs.  PSM3_PRINT_STATS now allows an optional pattern to enable statistics output for a subset of the processes in a job.  Added PSM3_PRINT_STATS_PREFIX and updated PSM3 Performance Statistics, PSM3_PRINT_STATS_HELP.  The use of colon to separate DSA work queue lists in PSM3_DSA_WQS has been deprecated, a semicolon is now used to separate DSA work queue lists in PSM3_DSA_WQS has been deprecated, a semicolon is now used to separate DSA work queue lists in PSM3_DSA_WQS has been deprecated, and PSM3_PRINT_STATS_HELP.  The use of colon to separate DSA work queue lists in PSM3_GPU_THRESH_RNDV_PSM3_MR_CACHE_MODE, PSM3_MQ_RNDV_NIC_WINDOW. Updated Multi-Rail Environment Variables, PSM3_Verbs RDMA Mo | Improved PSM3_FLOW_CREDITS to have a better flow control for RC verbs     Improved PSM3_MTU to allow a value larger than NIC MTU for RC verbs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ary 2025 1.10 |

| <ul> <li>Added new GPU aware NIC selection algorithms. See Multi-Rail Environment Variables, Multi-Rail Configuration Examples, PSM3 Multi-IP Environment Variables, PSM3 Multi-IP Configuration Examples, Building the PSM3 RPM, PSM3_MULTIRAIL, PSM3_MULTIRAIL_MAP, and PSM3_NIC_SELECTION_ALG.</li> <li>PSM3_MULTIRAIL_MAP now allows for per process selection of NICs. Also updated Multi-Rail Environment Variables, Multi-Rail Configuration Examples, and PSM3 Multi-IP Environment Variables.</li> <li>Documented Intel MPI support of NVIDIA GPUs, see Using PSM3 Features for NVIDIA GPUDirect.</li> <li>Documented Intel MPI setting of PSM3_GPUDIRECT in Environment Variables for Intel® MPI Library Jobs, Using PSM3 Features for Direct Access to Intel GPUs, Using PSM3 Features for NVIDIA GPUDirect, and PSM3_GPUDIRECT.</li> <li>Changes to default for PSM3_GPUDIRECT_RDMA_RECV_LIMIT and PSM3_GPUDIRECT_RDMA_SEND_LIMIT for Intel GPUs.</li> <li>PSM3_PRINT_STATS now allows an optional pattern to enable statistics output for a subset of the processes in a job.</li> <li>Added PSM3_PRINT_STATS and PSM3_PRINT_STATS_HELP.</li> <li>The use of colon to separate DSA work queue lists in PSM3_DSA_WQS has been deprecated, a semicolon is now used to separate DSA work queue lists.</li> <li>Added PSM3_RNDV_NIC_WINDOW and PSM3_GPU_RNDV_NIC_WINDOW and PSM3_GPU_RNDV_NIC_WINDOW and PSM3_GPU_RNDV_NIC_WINDOW. Updated Multi-Rail Environment Variables, PSM3_WR_NOW_NIC_WINDOW. Updated Multi-Rail Environment Variables, PSM3_WR_DRNDV_NIC_WINDOW. PSM3_MR_CACHE_SIZE.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Default for PSM3_RDMA is now 1 when rendezvous module is available or PSM3_GPUDIRECT is enabled.      PSM3_FLOW_CREDITS now allows dynamic credit adjustment bas on network behavior.      Default for PSM3_MQ_RNDV_SHM_GPU_THRESH is now 63 for                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2024 1.9      |

| continued                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Added new GPU aware NIC selection algorithms. See Multi-Rail Environment Variables, Multi-Rail Configuration Examples, PSM3 Multi-IP Environment Variables, PSM3 Multi-IP Configuration Examples, Building the PSM3 RPM, PSM3_MULTIRAIL, PSM3_MULTIRAIL, PSM3_MULTIRAIL_MAP, and PSM3_NIC_SELECTION_ALG.  PSM3_MULTIRAIL_MAP now allows for per process selection of NIC Also updated Multi-Rail Environment Variables, Multi-Rail Configuration Examples, and PSM3 Multi-IP Environment Variables  Documented Intel MPI support of NVIDIA GPUS, see Using PSM3 Features for NVIDIA GPUDirect.  Documented Intel MPI setting of PSM3_GPUDIRECT in Environment Variables for Intel® MPI Library Jobs, Using PSM3 Features for Dir Access to Intel GPUS, Using PSM3 Features for NVIDIA GPUDirect, and PSM3_GPUDIRECT.  Changes to default for PSM3_GPUDIRECT_RDMA_RECV_LIMIT and PSM3_GPUDIRECT_RDMA_SEND_LIMIT for Intel GPUs.  PSM3_GPUDIRECT_RDMA_SEND_LIMIT for Intel GPUs.  PSM3_GPUDIRECT_RDMA_SEND_LIMIT for Intel GPUS.  Added PSM3_PRINT_STATS now allows an optional pattern to enable statistics output for a subset of the processes in a job.  Added PSM3_RRINT_STATS_PREFIX and updated PSM3 Performan Statistics, PSM3_PRINT_STATS_ PREFIX and updated PSM3_PRINT_STATS_HELP.  The use of colon to separate DSA work queue lists in PSM3_DSA_WQS has been deprecated, a semicolon is now used t separate DSA work queue lists.  Added PSM3_RNDV_NIC_WINDOW and deprecated PSM3_MQ_RNDV_NIC_WINDOW. Updated Multi-Rail Environment Variables, PSM3_GPU_THRESH_RNDV, PSM3_MR_CACHE_MODE, PSM3_MR_CACHE_SIZE_MB, PSM3_MTIV, | h 2024 1.8    |

June 2025

Doc. No.: 632489, Rev.: 1.11

User Guide

3

| Date           | Revision | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|----------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                |          | Added PSM3_MQ_RNDV_SHM_GPU_THRESH and updated PSM3_MQ_RNDV_SHM_THRESH.      Default for PSM3_GPU_THRESH_RNDV when using sockets HAL is                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                |          | now 4GB.  • PSM3_GPUDIRECT_RDMA_RECV_LIMIT, PSM3_GPUDIRECT_RDMA_SEND_LIMIT, and PSM3_GPU_THRESH_RNDV allow input of max.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                |          | PSM3_UDP_GSO now allows direct control over the maximum segmentation offload size.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                |          | Correctly document default for PSM3_GPUDIRECT_RDMA_SEND_LIMIT for NVIDIA GPUs.  Transported descriptions of anyting property of the property in the property of the prope    |

|                |          | Improved descriptions of environment variable reporting in<br>PSM3_PRINT_STATSMASK and PSM3_VERBOSE_ENV.      STATSMASK and PSM3_VERBOSE_ENV.      The state of |

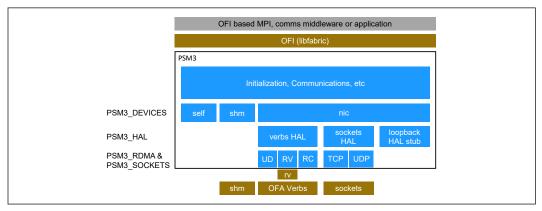

|                |          | Improved description of PSM3_DEVICES and PSM3 Architecture and<br>Hardware Abstraction Layer.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                |          | Added Confirming the PSM3 Provider is Selected and referenced in<br>Running MPI Applications with Intel® MPI Library, Running Open<br>MPI Applications, Running Applications that Use oneCCL, Running<br>with oneCCL, and Running with NVIDIA NCCL.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                |          | Improved description of ethbw.     Improved description in PSM3 Rendezvous Kernel Module.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                |          | Added discussion ofenable-psm3-dsa andenable-psm3-<br>umr-cache build options as well as use of Intel icx compiler to<br>Building the PSM3 RPM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| September 2023 | 1.7      | Product 11.5.1.0 release - Changes to this document include:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                |          | Documented PSM3_GPUDIRECT_RDMA_RECV_LIMIT.     Changes to default for PSM3_GPUDIRECT_RDMA_SEND_LIMIT and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                |          | PSM3_MQ_RNDV_NIC_WINDOW for Intel GPU.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                |          | Added PSM3_IDENTIFY output of GPU library versions.     NVIDIA GPU cross version interoperability improved. See Building                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                |          | the PSM3 RPM.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                |          | Added new compilers in Compiling MPI Applications with Intel® MPI Library.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                |          | <ul> <li>Updated example in Running with Multiple PSM3 Variations.</li> <li>Improved description of user space MR cache performance analysis.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                |          | See PSM3 Performance Statistics  Improved description of PSM3_TRACEMASK and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                |          | PSM3_DEBUG_FILENAME.  • Assorted grammatical, formatting and style improvements through                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                |          | the document.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| May 2023       | 1.6      | Product 11.5.0.0 release - Changes to this document include:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                |          | Documented the user space MR cache. See PSM3 Verbs RDMA<br>Modes and Rendezvous Module, PSM3 Rendezvous Kernel Module,<br>PSM3_MR_CACHE_MODE, PSM3_MR_CACHE_SIZE and<br>PSM3_MR_CACHE_SIZE_MB.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                |          | Intel® Xeon® Processor Data Streaming Accelerator (DSA) shared work queue support added and discussed in the following sections: PSM3 Data Streaming Accelerator Support, PSM3_DSA_MULTI, PSM3_DSA_WQS, PSM3_IDENTIFY and dsa_setup.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                |          | Documented additional settings for running Intel GPU applications.     See PSM3 and Intel GPU Support and Intel GPU Application Failures.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                |          | Documented new PSM3_PRINT_STATSMASK bit of 0x40 to include process launch information. Also see PSM3 Performance Statistics.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                |          | Documented additional PSM3 defaults which may be overridden by the Intel® MPI Library. See Environment Variables for Intel® MPI Library Jobs and PSM3_HAL.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                |          | Added additional suggested debug procedures in MPI Job Failures     Due to Initialization Problems.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |